OMRON FQM1 Motion Controller Instruction System

The OMRON FQM1 series flexible motion controller, as a core component in the field of industrial automation, provides a solid foundation for modern FA (factory automation) systems with its powerful instruction set and flexible system architecture. This article is based on the instruction reference manual of the FQM1 series (covering FQM-1-CM002, FQM1-MMP22, and FQM1-MMA22 models), and deeply analyzes its technical specifications, safety guidelines, version evolution, and programming instruction details, aiming to provide a detailed professional technical guide for electrical engineers and system designers.

System Overview and Security Standards

The FQM1 series controller consists of a coordination module and a motion control module, designed to meet complex motion control and logic control requirements. As a professional industrial equipment, its operation and maintenance are strictly limited to professionals with electrical engineering knowledge. The manual clearly defines safety risks through three levels: “DANGER”, “Warning”, and “Caution”.

At the operational level, the manual emphasizes several crucial safety principles:

Electric shock protection: It is strictly prohibited to disassemble modules or touch terminals while powered on, as this may cause serious electric shock injuries.

External safety circuit: Given that the controller may experience output abnormalities (such as output locking in ON or OFF state) due to hardware failures or self diagnostic errors, the system design must include external physical safety circuits (such as emergency stop circuits, interlock circuits) to ensure safe shutdown of the system in the event of controller failure.

Grounding requirements: During installation, a grounding resistor of less than 100 Ω must be connected, especially when the functional grounding of the power unit is short circuited to the grounding terminal of the line. Good grounding must be ensured to prevent electric shock or interference.

In addition, the manual also provides detailed environmental precautions for operation, prohibiting operation in direct sunlight, condensation, corrosive gases, or strong electromagnetic fields. It emphasizes the use of crimping terminals during wiring to avoid direct connection of exposed stranded wires and prevent short circuits or fire risks.

Unit version and functional evolution

The FQM1 series controllers undergo iteration and hardware upgrades through the “unit version” management function. The version number is usually marked to the right of the batch number on the module nameplate. From version 2.0 to 3.3, the controller has undergone significant feature enhancements:

Version 3.1: The main improvement lies in obtaining UL certification, which requires the configuration of specific relay units and connecting cables to comply with safety standards.

Version 3.2: Introduced multiple key features. In electronic cam mode, PULS (886) command supports pulse output zero crossing (CW/CCW direction) and can automatically calculate the pulse output frequency. In addition, a cyclic refresh zone has been added for data exchange between modules, and support for CJ series units has been expanded, such as analog output units (CJ1W-DA08V, etc.) and position control units. In the system settings, the output range of the 20MHz clock frequency can be extended to 1 Hz to 1 MHz, greatly improving the low-frequency control accuracy.

Version 3.3: The focus has been on enhancing compatibility with servo motors, starting to support OMNUC G-series absolute encoders, and further expanding the mounting capability of CJ series special I/O units, including analog input/output units and hybrid modules.

These version differences require engineers to verify module versions when designing systems to ensure that software instructions match hardware functionality.

Fundamentals of Programming and Data Structures

The program capacity of FQM1 varies depending on the module type, and the coordination module (CM002) has 10K steps. Programming adopts ladder logic, and instruction execution involves bit processing and word processing. Understanding data formats and addressing methods is a prerequisite for efficient programming.

1. Data format

FQM1 supports multiple data formats, including unsigned binary, signed binary, BCD code, and floating-point numbers. Floating point numbers follow the IEEE754 standard, support single precision and double precision operations, and are widely used in high-precision mathematical operation instructions. Binary negative numbers are represented using complement codes, which is crucial for understanding the results of arithmetic operations.

2. operands and addressing

Instructions typically include source operands, target operands, and control operands.

Bit address: Specify the word address and bit number (such as 0001.02).

Indirect addressing: Supports binary mode (@ D) and BCD mode (* D). For example, @ D00300 represents using the content of D00300 as a new address pointer, greatly enhancing the flexibility of the program.

Constant input: Supports decimal (&prefix) and hexadecimal (# prefix), but in timer/counter settings, constant input must conform to the BCD code range.

3. Differential instruction

To capture the edge changes of the signal, FQM1 provides non differential, rising edge differential (@ prefix), and falling edge differential (% prefix) instructions. The rising edge differentiation is only executed once when the execution condition changes from OFF to ON, while the falling edge differentiation is the opposite. This plays a crucial role in handling trigger signals and avoiding duplicate execution.

Detailed Explanation of Core Instruction Set

The instruction set of FQM1 is large and finely classified. The following focuses on analyzing the key instruction categories.

1. Sequential input instructions

This is the cornerstone of ladder diagram programming. LD (load), AND (AND), OR (OR), and their NOT forms form the basis of logical judgment.

Logical block connection: The AND LD and OR LD instructions are used to connect complex logical blocks. The manual states that when using these instructions to connect multiple logical blocks, the number of LOAD instructions must be one more than AND LD/OR LD instructions, otherwise it will cause programming errors.

Bit test instructions: TST (350) and TSTN (351) allow testing of specific bit states in specified words like LD/AND/OR, and support DM area operations, solving the limitation of traditional contact instructions that cannot directly read DM areas.

Conditional on-off: The UP (521) and DOWN (522) instructions simplify differential logic and can generate single cycle pulses without occupying working bits, which helps streamline program steps.

2. Sequential output instructions

Output and hold: The OUT instruction directly outputs the state of the execution condition, while the KEEP (011) instruction implements the function of a latch relay. Set when Set input is ON, reset when Reset input is ON. It should be noted that in the interlock program segment, the KEEP instruction can maintain the state, while the ordinary self holding circuit will reset due to the release of the interlock.

Set and Reset: The SET and RSET instructions are independent of execution conditions and only change the bit state when the condition is ON, and remain unchanged when it is OFF. In contrast, the SETB (532), RSTB (533), and OUTB (534) instructions not only operate on the DM location, but also support immediate refreshing of variants (! Prefix), which can directly update physical output terminals and shorten response time.

3. Sequential control instructions

Interlock: IL (002) and ILC (003) must be used in pairs. When the IL condition is OFF, the program segment output between IL and ILC is forcibly reset (OUT becomes OFF, TIM is reset), but the SET/RSET and counter states remain unchanged. This is different from the JMP instruction, as all output states in the program segments skipped by JMP remain unchanged.

Jump: JMP (004)/JME (005) pairs are used to skip program segments. When the JMP condition is OFF, a jump occurs and the skipped instruction is not executed, resulting in a shorter loop time. CJP (510) jumps when the condition is ON, while CJPN (511) is similar to JMP. Note that jump instructions must be paired and within the same task.

Loop: FOR (512)/NEXT (513) forms a loop structure, and the value of N determines the number of loops. The BREAK (514) instruction can be used to forcefully exit a loop. The nested depth of the loop is limited to 15 layers and cannot cross tasks.

4. Timer and counter instructions

FQM1 provides multiple precision timers:

TIM: Standard 100ms countdown timer with an accuracy of -0.01s~0s.

TIMH (015): High speed 10ms countdown timer.

TMHH (540): Ultra high precision 1ms countdown timer, whose current value refreshes every 1ms through interrupts, suitable for microsecond level control requirements.

CNTR (012): Reversible counter with up and down inputs, suitable for scenarios such as position accumulation.

The manual specifically states that in the jump program segment, the timer that is currently counting will continue to count; In the interlock program segment, the timer will be reset. This is because the IL instruction forces a reset of the output state, while JMP only skips execution logic.

5. Data processing and operation instructions

Although the source data in this article does not fully cover all operation instructions, the full picture can be seen from the instruction list.

Comparison instructions: In addition to basic CMP, there are also symbol comparison instructions (such as LD>, AND<=, etc.) as well as table comparison (TCMP) and block comparison (BCMP). The block comparison BCMP (068) can determine whether the source data is within the preset upper and lower limits, greatly simplifying the logic of multi interval judgment.

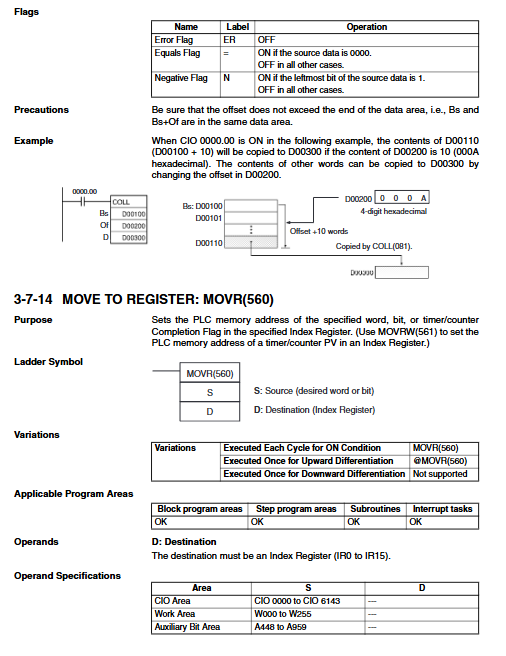

Data movement: The MOV instruction family supports the transfer of words, bits, and digits. XCHG (073) is used for data exchange, XFER (070) is used for block transfer, and BSET (071) is used for memory filling.

Mathematical operations: Supports BCD code and binary arithmetic operations, including carry processing. Floating point operation instructions (such as+F, * F) comply with the IEEE754 standard, support trigonometric and exponential logarithmic operations, and meet the requirements of complex algorithms.

Logical operations: Instructions such as ANDW, ORW, XORW are used for bitwise logical operations on word data, commonly used for masking or extracting status words.

Advanced features and system maintenance

FQM1 has a comprehensive self diagnostic function. FAL (006) is used for non fatal error alarms, and the system continues to operate; FALS (007) indicates a fatal error and will stop the controller from running. These instructions, in conjunction with the flag bits in the auxiliary area (Area A), provide convenience for troubleshooting.

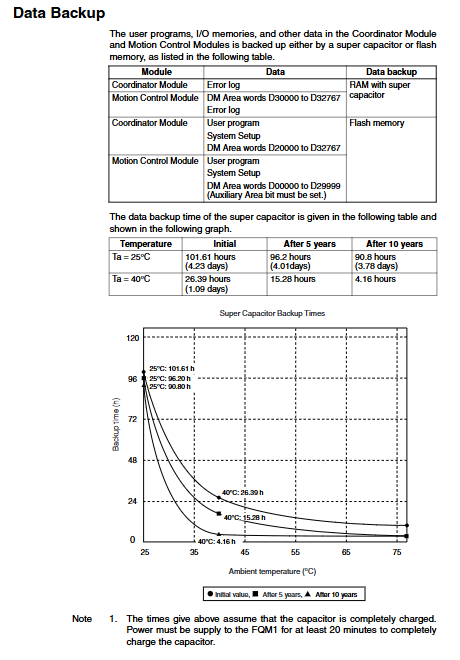

In terms of data backup mechanism, the user program and some DM areas of the coordination module are backed up through Flash memory, while some DM areas and error logs of the motion control module rely on supercapacitors. At 25 ° C, the capacitor backup time can reach about 100 hours, but as the ambient temperature increases and the lifespan increases, the backup time will be shortened. Therefore, for data recovery after long-term power outages, it is recommended to store key parameters in the DM area address supported by Flash (D20000-D32767).